PRELIMINARY

# CYP32G0401DX

# Multi-Gigabit Multi-Mode Quad HOTLink-III™ Transceiver

### Features

- Third-generation HOTLink<sup>®</sup> technology

- 2488- to 3125-Mbps signaling rate per serial link

- XAUI/10G Ethernet compatible mode

- InfiniBand™ compatible

- Programmable 8-bit or 10-bit SERDES

- Selectable 8B/10B encoding/decoding

- Ethernet PCS functions using the IEEE802.3z ordered set state machine

- Programmable receive framer provides alignment to — A1/A2: SONET/SDH

- 8B/10B COMMA: Ethernet, InfiniBand, XAUI

- Synchronous SSTL\_2 parallel input/output interface

- Internal PLLs with no external PLL components

- Differential CML serial inputs per channel

- Differential CML serial outputs per channel

- Source matched for 50  $\Omega$  transmission lines

- -No external bias resistors required

- Compatible with

- Fiber-optic modules

- Copper cables

- Circuit board traces

- · Diagnostic loop back and line loop back

- · Signal detect input

- Low Power (2.5W typical)

- -Single +2.5V V<sub>DD</sub> supply

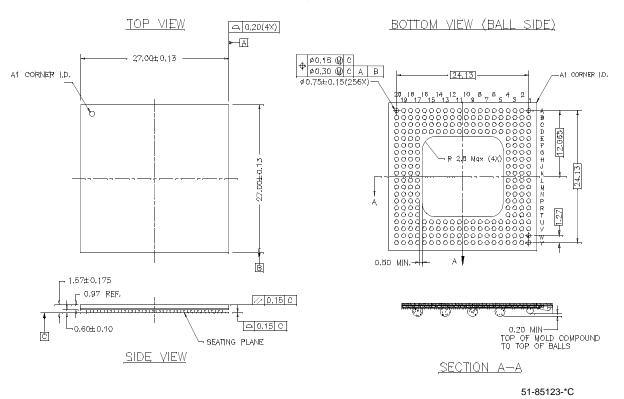

- 256-ball Thermally Enhanced BGA

- Commercial temperature range 0°C to +70°C

- Industrial temperature range –40°C to +85°C

## **Functional Description**

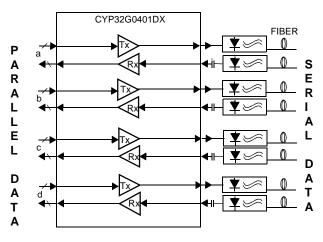

The CYP32G0401DX Quad HOTLink-III™ Transceiver is a point-to-point communications building block allowing the transfer of data over high-speed serial links (optical fiber, balanced, and unbalanced copper transmission lines) at signaling speeds ranging from 2488 to 3125 Mbps per serial link.

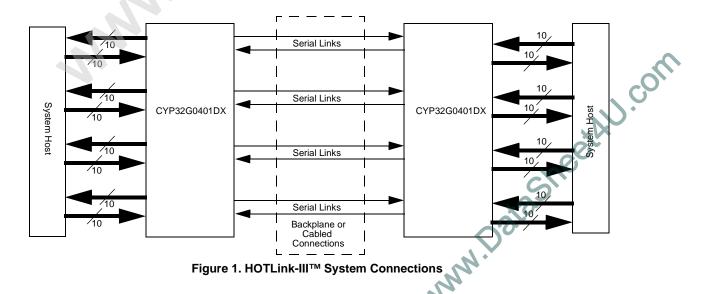

Each transmit channel accepts parallel characters in an Input Register, encodes each character for transport, and converts it to serial data. Each receive channel accepts serial data and converts it to parallel data, decodes the data into characters, and presents these characters to an output register. *Figure 1* illustrates typical connections between independent host systems and corresponding CYP32G0401DX parts. As a thirdgeneration HOTLink transceiver, the CYP32G0401DX extends the HOTLink family with enhanced levels of integration, multi-gigabit data rates, and multi-mode versatility.

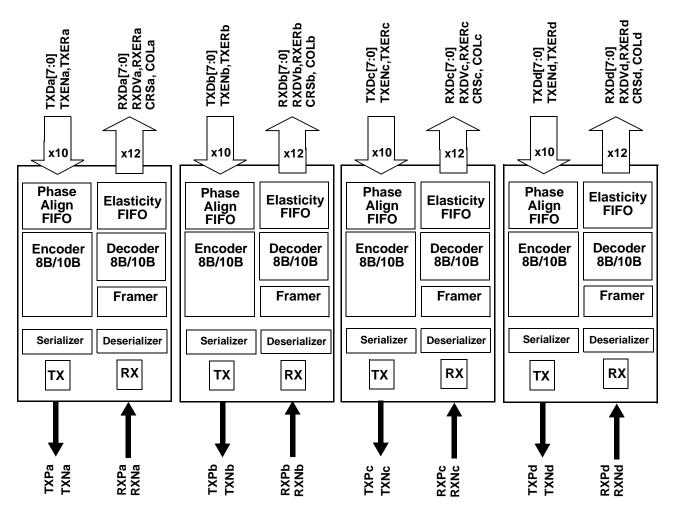

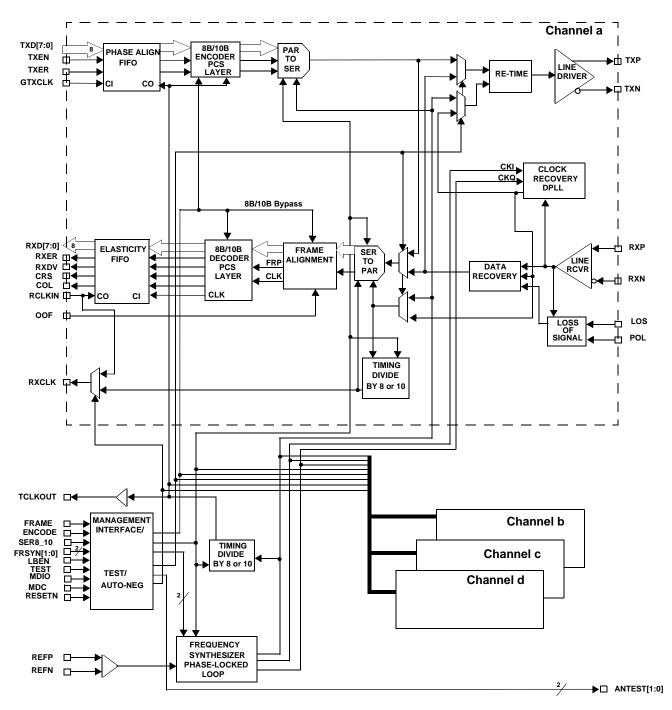

The transmit section of the CYP32G0401DX Quad HOTLink-III shown in *Figure 2* consists of four channels. Each channel can accept either 8-bit data characters or pre-encoded 10-bit transmission characters. Data characters are passed from the Transmit Input Register to an embedded bypassable 8B/10B Encoder to improve their serial transmission characteristics. These encoded characters are then serialized and output from Current Mode Logic (CML) differential transmission-line drivers at a bit-rate which is a multiple of the input reference clock.

The receive section of the CYP32G0401DX Quad HOTLink-III consists of four channels. Each channel accepts a serial bitstream from a CML differential line receiver and, using a completely integrated PLL Clock Synchronizer, recovers the timing information necessary for data reconstruction. Each recovered bit-stream is deserialized and framed into characters, 8B/10B decoded, and checked for transmission errors. Recovered decoded characters are then written to an internal Elasticity Buffer, and presented to the destination host system. The integrated 8B/10B encoder/decoder may be bypassed for systems that present externally encoded or scrambled data at the parallel interface.

et • San Jose

The parallel I/O interface may be configured for numerous forms of clocking to provide the highest flexibility in system architecture. The receive interface may be configured to present data relative to a recovered clock (output) or to a local reference clock (input). The CYP32G0401DX is illustrated in greater detail in *Figure 3*.

HOTLink-III devices are ideal for a variety of applications where parallel interfaces can be replaced with high-speed, point-to-point serial links. Some applications include interconnecting workstations, backplanes, servers, mass storage, and video transmission equipment.

Figure 2. CYP32G0401DX Transceiver Logic Block Diagram

Figure 3. CYP32G0401DX Transceiver Block Diagram

## Pin Configuration (Top View)

|   | 1       | 2       | 3      | 4       | 5     | 6      | 7       | 8     | 9     | 10    | 11      | 12      | 13    | 14    | 15      | 16    | 17     | 18    | 19      | 20      |

|---|---------|---------|--------|---------|-------|--------|---------|-------|-------|-------|---------|---------|-------|-------|---------|-------|--------|-------|---------|---------|

| A | DGND    | DGND    | DGND   | RCLKINc | RXD2c | RXCLKc | GTXCLKc | TXD5c | DGND  | DGND  | TCLKOUT | GTXCLKb | DGND  | TXD4b | RCLKINb | RXD7b | RXCLKb | DGND  | DGND    | DGND    |

| в | DGND    | DVDD    | DVDD   | RXD5c   | RXD3c | RXD0c  | TXD1c   | TXD3c | TXD7c | TXENc | VDIGCc  | TXD0b   | TXD2b | TXD5b | RXDVb   | RXD6b | RXD4b  | DVDD  | DVDD    | DGND    |

| С | DGND    | DVDD    | DVDD   | RXD7c   | RXD4c | RXD1c  | COLc    | TXD2c | TXD6c | TXERc | TSYNC   | TXD1b   | TXD3b | TXD7b | TXENb   | RXD5b | RXD3b  | DVDD  | DVDD    | DGND    |

| D | OOFd    | RXDVc   | RXERc  | DVDD    | RXD6c | CRSc   | DVDD    | TXD0c | TXD4c | DVDD  | GDIGCc  | GDIGCb  | TXD6b | DVDD  | TXERb   | RXERb | DVDD   | RXD2b | RXD1b   | RXD0b   |

| Е | RXCLKd  | RXD7d   | RXDVd  | OOFc    |       |        |         |       |       |       |         |         |       |       |         |       | COLb   | CRSb  | OOFa    | RXCLKa  |

| F | RXD4d   | RXD5d   | RXD6d  | RXERd   |       |        |         |       |       |       |         |         |       |       |         |       | OOFb   | RXDVa | RXERa   | RXD7a   |

| G | RCLKINd | RXD2d   | RXD3d  | GDIGCd  |       |        |         |       |       |       |         |         |       |       |         |       | GDIGCa | RXD6a | RXD4a   | RXD3a   |

| н | DGND    | RXD0d   | RXD1d  | COLd    |       |        |         |       |       |       |         |         |       |       |         |       | RXD5a  | RXD2a | CRSa    | RCLKINa |

| J | GTXCLKd | TXD1d   | TXD0d  | CRSd    |       |        |         |       |       |       |         |         |       |       |         |       | RXD1a  | RXD0a | COLa    | DGND    |

| к | TXD5d   | TXD4d   | TXD3d  | TXD2d   |       |        |         |       |       |       |         |         |       |       |         |       | DVDD   | TXD0a | GTXCLKa | DGND    |

| L | DGND    | TXD7d   | TXD6d  | VDIGCd  |       |        |         |       |       |       |         |         |       |       |         |       | TXD4a  | TXD3a | TXD2a   | TXD1a   |

| М | DGND    | TXENd   | DVDD   | TXERd   |       |        |         |       |       |       |         |         |       |       |         |       | TXENa  | TXD7a | TXD6a   | TXD5a   |

| N | RESETN  | TEST    | FRSYN1 | FRSYN0  |       |        |         |       |       |       |         |         |       |       |         |       | MDIO   | TXERa | VDIGCa  | DGND    |

| Ρ | ANTEST0 | ANTEST1 | GTXMc  | AVDD    |       |        |         |       |       |       |         |         |       |       |         |       | AVDD   | VRXMb | MDC     | VDIGCb  |

| R | REFP    | VTXMc   | VRXMc  | GTXMd   |       |        |         |       |       |       |         |         |       |       |         |       | VTXMb  | TRS   | ТСК     | TMS     |

| т | REFN    | GRXMc   | VTXMd  | VRXMd   |       |        |         |       |       |       |         |         |       |       |         |       | GRXMa  | GTXMb | TDI     | TDO     |

| U | GRXMd   | ENCODE  | FRAME  | AVDD    | LOSd  | GRXDd  | AVDD    | TXNd  | TXPd  | GTXDc | VTXDb   | TXNa    | TXPa  | AVDD  | GRXDa   | GTXMa | AVDD   | VRXMa | LBEN    | GRXMb   |

| V | AGND    | AVDD    | AVDD   | SER8_10 | LOSc  | POLd   | GRXDc   | GTXDd | TXNc  | TXPc  | TXPb    | TXNb    | GTXDa | GRXDb | VRXDa   | LOSb  | POLa   | AVDD  | AVDD    | AGND    |

| W | AGND    | AVDD    | AVDD   | VRXDd   | RXNd  | RXPd   | VTXDd   | GFS3  | VTXDc | GFS1  | VFS2    | GTXDb   | VTXDa | VRXDb | RXNa    | RXPa  | VTXMa  | AVDD  | AVDD    | AGND    |

| Y | AGND    | AGND    | AGND   | POLc    | VRXDc | RXNc   | RXPc    | AGND  | VFS3  | VFS1  | AGND    | AGND    | GFS2  | RXNb  | RXPb    | POLb  | LOSa   | AGND  | AGND    | AGND    |

# Pin Configuration (Bottom View)

| 20      | 19      | 18    | 17     | 16    | 15      | 14    | 13    | 12      | 11      | 10    | 9     | 8     | 7       | 6      | 5     | 4       | 3      | 2       | 1       |   |

|---------|---------|-------|--------|-------|---------|-------|-------|---------|---------|-------|-------|-------|---------|--------|-------|---------|--------|---------|---------|---|

| DGND    | DGND    | DGND  | RXCLKb | RXD7b | RCLKINb | TXD4b | DGND  | GTXCLKb | TCLKOUT | DGND  | DGND  | TXD5c | GTXCLKc | RXCLKc | RXD2c | RCLKINc | DGND   | DGND    | DGND    | А |

| DGND    | DVDD    | DVDD  | RXD4b  | RXD6b | RXDVb   | TXD5b | TXD2b | TXD0b   | VDIGCc  | TXENc | TXD7c | TXD3c | TXD1c   | RXD0c  | RXD3c | RXD5c   | DVDD   | DVDD    | DGND    | в |

| DGND    | DVDD    | DVDD  | RXD3b  | RXD5b | TXENb   | TXD7b | TXD3b | TXD1b   | TSYNC   | TXERc | TXD6c | TXD2c | COLc    | RXD1c  | RXD4c | RXD7c   | DVDD   | DVDD    | DGND    | с |

| RXD0b   | RXD1b   | RXD2b | DVDD   | RXERb | TXERb   | DVDD  | TXD6b | GDIGCb  | GDIGCc  | DVDD  | TXD4c | TXD0c | DVDD    | CRSc   | RXD6c | DVDD    | RXERc  | RXDVc   | OOFd    | D |

| RXCLKa  | OOFa    | CRSb  | COLb   |       |         |       |       |         |         |       |       |       |         |        |       | OOFc    | RXDVd  | RXD7d   | RXCLKd  | Е |

| RXD7a   | RXERa   | RXDVa | OOFb   |       |         |       |       |         |         |       |       |       |         |        |       | RXERd   | RXD6d  | RXD5d   | RXD4d   | F |

| RXD3a   | RXD4a   | RXD6a | GDIGCa |       |         |       |       |         |         |       |       |       |         |        |       | GDIGCd  | RXD3d  | RXD2d   | RCLKINd | G |

| RCLKINa | CRSa    | RXD2a | RXD5a  |       |         |       |       |         |         |       |       |       |         |        |       | COLd    | RXD1d  | RXD0d   | DGND    | н |

| DGND    | COLa    | RXD0a | RXD1a  |       |         |       |       |         |         |       |       |       |         |        |       | CRSd    | TXD0d  | TXD1d   | GTXCLKd | J |

| DGND    | GTXCLKa | TXD0a | DVDD   |       |         |       |       |         |         |       |       |       |         |        |       | TXD2d   | TXD3d  | TXD4d   | TXD5d   | к |

| TXD1a   | TXD2a   | TXD3a | TXD4a  |       |         |       |       |         |         |       |       |       |         |        |       | VDIGCd  | TXD6d  | TXD7d   | DGND    | L |

| TXD5a   | TXD6a   | TXD7a | TXENa  |       |         |       |       |         |         |       |       |       |         |        |       | TXERd   | DVDD   | TXENd   | DGND    | м |

| DGND    | VDIGCa  | TXERa | MDIO   |       |         |       |       |         |         |       |       |       |         |        |       | FRSYN0  | FRSYN1 | TEST    | RESETN  | N |

| VDIGCb  | MDC     | VRXMb | AVDD   |       |         |       |       |         |         |       |       |       |         |        |       | AVDD    | GTXMc  | ANTEST1 | ANTEST0 | Р |

| TMS     | ТСК     | TRS   | VTXMb  |       |         |       |       |         |         |       |       |       |         |        |       | GTXMd   | VRXMc  | VTXMc   | REFP    | R |

| TDO     | TDI     | GTXMb | GRXMa  |       |         |       |       |         |         |       |       |       |         |        |       | VRXMd   | VTXMd  | GRXMc   | REFN    | т |

| GRXMb   | LBEN    | VRXMa | AVDD   | GTXMa | GRXDa   | AVDD  | TXPa  | TXNa    | VTXDb   | GTXDc | TXPd  | TXNd  | AVDD    | GRXDd  | LOSd  | AVDD    | FRAME  | ENCODE  | GRXMd   | U |

| AGND    | AVDD    | AVDD  | POLa   | LOSb  | VRXDa   | GRXDb | GTXDa | TXNb    | TXPb    | TXPc  | TXNc  | GTXDd | GRXDc   | POLd   | LOSc  | SER8_10 | AVDD   | AVDD    | AGND    | v |

| AGND    | AVDD    | AVDD  | VTXMa  | RXPa  | RXNa    | VRXDb | VTXDa | GTXDb   | VFS2    | GFS1  | VTXDc | GFS3  | VTXDd   | RXPd   | RXNd  | VRXDd   | AVDD   | AVDD    | AGND    | w |

| AGND    | AGND    | AGND  | LOSa   | POLb  | RXPb    | RXNb  | GFS2  | AGND    | AGND    | VFS1  | VFS3  | AGND  | RXPc    | RXNc   | VRXDc | POLc    | AGND   | AGND    | AGND    | Y |

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guide-lines, not tested.)

| Storage Temperature65°C to +150°C                                                           |

|---------------------------------------------------------------------------------------------|

| Ambient Temperature with<br>Power Applied55°C to +100°C                                     |

| Supply Voltage to Ground Potential0.5V to +3.0V                                             |

| DC Voltage Applied on Any Pin with Respect to Ground                                        |

| (with $V_{\text{DD}}$ in Normal Operating Range)–0.5V to $V_{\text{DD}}\text{+}0.5\text{V}$ |

## **Pin Descriptions**

## CYP32G0401DX Transmitter Pins (53)<sup>[1]</sup>

| Static Discharge Voltage> 500 V<br>(per JEDEC) |

|------------------------------------------------|

| Latch-Up Current> 200 mA                       |

#### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>DD</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | +2.5V ±5%       |

| Industrial | –40°C to +85°C         | +2.5V ±5%       |

| Pin                                          | Name                                                         | Level  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|--------------------------------------------------------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

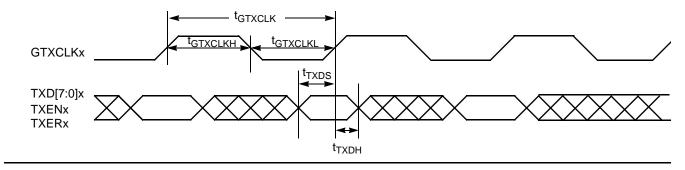

| K18, L20<br>L19, L18<br>L17, M20<br>M19, M18 | TXD0a, TXD1a<br>TXD2a, TXD3a<br>TXD4a, TXD5a<br>TXD6a, TXD7a | SSTL_2 | inputs | Channel a transmit data in. The transmit data TXDa[7:0] are clocked into the Phase Align FIFO on the rising edge of the GTXCLKa signal. The data are read out of the Phase Align FIFO with TCLKOUT. The phase of GTXCLKa may differ from that of TCLKOUT by any amount. In <b>MODE</b> $1^{[1]}$ the frequency of GTXCLKa may differ from that of TCLKOUT by up to 200 ppm. |

| M17                                          | TXENa                                                        | SSTL_2 | input  | Channel a transmit enable (TXENa) in <i>MODE 1</i><br>Channel a transmit data bit 8 (TXD8a) in <i>MODE 2</i><br>Not used in <i>MODE 3</i> (Suggest user drive to zero)<br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                            |

| N18                                          | TXERa                                                        | SSTL_2 | input  | Channel a transmit error (TXERa) in <i>MODE 1</i><br>Channel a transmit data bit 9 (TXD9a) in <i>MODE 2</i><br>Channel a transmit code-group select (TXKa) in <i>MODE 3</i><br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                       |

| K19                                          | GTXCLKa                                                      | SSTL_2 | input  | Channel a transmit clock. The rising edge of GTXCLKa clocks the input data into the Phase Align FIFO.                                                                                                                                                                                                                                                                       |

| U13                                          | ТХРа                                                         | CML    | output | Channel a differential serial data transmit. TXPa is the positive differential output pin of the channel a Line Driver. The TXPa and TXNa look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                           |

| U12                                          | TXNa                                                         | CML    | output | Channel a differential serial data transmit. TXNa is the negative differential output pin of the channel a Line Driver. The TXPa and TXNa look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                           |

| B12, C12<br>B13, C13<br>A14, B14<br>D13, C14 | TXD0b, TXD1b<br>TXD2b, TXD3b<br>TXD4b, TXD5b<br>TXD6b, TXD7b | SSTL_2 | inputs | Channel b transmit data in. The transmit data TXDb[7:0] are clocked into the Phase Align FIFO on the rising edge of the GTX-CLKb signal. The data are read out of the Phase Align FIFO with TCLKOUT. The phase of GTXCLKb may differ from that of TCLK-OUT by any amount. In <b>MODE 1</b> the frequency of GTXCLKb may differ from that of TCLKOUT by up to 200 ppm.       |

| C15                                          | TXENb                                                        | SSTL_2 | input  | Channel b transmit enable (TXENb) in <i>MODE 1</i><br>Channel b transmit data bit 8 (TXD8b) in <i>MODE 2</i><br>Not used in <i>MODE 3</i> (Suggest user drive to zero)<br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                            |

| D15                                          | TXERb                                                        | SSTL_2 | input  | Channel b transmit error (TXERb) in <i>MODE 1</i><br>Channel b transmit data bit 9 (TXD9b) in <i>MODE 2</i><br>Channel b transmit code-group Select (TXKb) in <i>MODE 3</i><br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                       |

| A12                                          | GTXCLKb                                                      | SSTL_2 | input  | Channel b transmit clock. The rising edge of GTXCLKb clocks the input data into the Phase Align FIFO.                                                                                                                                                                                                                                                                       |

Note:

1. Transmitter pins are **MODE**-dependent where indicated. See Table 1 for defined **MODES** of operation.

## **Pin Descriptions**

# CYP32G0401DX Transmitter Pins (53)<sup>[1]</sup> (continued)

| Pin                                  | Name                                                         | Level  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------|--------------------------------------------------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V11                                  | ТХРЬ                                                         | CML    | output | Channel b differential Serial Data Transmit. TXPb is the positive differential output pin of the channel b Line Driver. The TXPb and TXNb look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                                      |

| V12                                  | TXNb                                                         | CML    | output | Channel b differential serial data transmit. TXNb is the negative differential output pin of the channel b Line Driver. The TXPb and TXNb look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                                      |

| D8, B7<br>C8, B8<br>D9, A8<br>C9, B9 | TXD0c, TXD1c<br>TXD2c, TXD3c<br>TXD4c, TXD5c<br>TXD6c, TXD7c | SSTL_2 | inputs | Channel c transmit data in. The transmit data TXDc[7:0] are<br>clocked into the Phase Align FIFO on the rising edge of the GTX-<br>CLKc signal. The data are read out of the Phase Align FIFO with<br>TCLKOUT. The phase of GTXCLKc may differ from that of TCLK-<br>OUT by any amount. In <b>MODE 1</b> the frequency of GTXCLKc may<br>differ from that of TCLKOUT by up to 200 ppm. |

| B10                                  | TXENc                                                        | SSTL_2 | input  | Channel c transmit enable (TXENc) in <i>MODE 1</i><br>Channel c transmit data bit 8 (TXD8c) in <i>MODE 2</i><br>Not used in <i>MODE 3</i> (Suggest user drive to zero)<br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                                       |

| C10                                  | TXERc                                                        | SSTL_2 | input  | Channel c transmit error (TXERc) in <i>MODE 1</i><br>Channel c transmit data bit 9 (TXD9c) in <i>MODE 2</i><br>Channel c transmit code-group select (TXKc) in <i>MODE 3</i><br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                                  |

| A7                                   | GTXCLKc                                                      | SSTL_2 | input  | Channel c transmit clock. The rising edge of GTXCLKc clocks the input data into the Phase Align FIFO.                                                                                                                                                                                                                                                                                  |

| V10                                  | ТХРс                                                         | CML    | output | Channel c differential serial data transmit. TXPc is the positive differential output pin of the channel c Line Driver. The TXPc and TXNc look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                                      |

| V9                                   | TXNc                                                         | CML    | output | Channel c differential serial data transmit. TXNc is the negative differential output pin of the channel c Line Driver. The TXPc and TXNc look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                                      |

| J3, J2<br>K4, K3<br>K2, K1<br>L3, L2 | TXD0d, TXD1d<br>TXD2d, TXD3d<br>TXD4d, TXD5d<br>TXD6d, TXD7d | SSTL_2 | inputs | Channel d transmit data in. The transmit data TXDd[7:0] are<br>clocked into the Phase Align FIFO on the rising edge of the GTX-<br>CLKd signal. The data are read out of the Phase Align FIFO with<br>TCLKOUT. The phase of GTXCLKd may differ from that of<br>TCLKOUT by any amount. In <b>MODE 1</b> the frequency of GTXCLKd<br>may differ from that of TCLKOUT by up to 200 ppm.   |

| M2                                   | TXENd                                                        | SSTL_2 | input  | Channel d transmit enable (TXENd) in <i>MODE 1</i><br>Channel d transmit data bit 8 (TXD8d) in <i>MODE 2</i><br>Not used in <i>MODE 3</i> (Suggest user drive to zero)<br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                                       |

| M4                                   | TXERd                                                        | SSTL_2 | input  | Channel d transmit error (TXERd) in <i>MODE 1</i><br>Channel d transmit data bit 9 (TXD9d) in <i>MODE 2</i><br>Channel d transmit code-group select (TXKd) in <i>MODE 3</i><br>Not used in <i>MODE 4</i> (Suggest user drive to zero)                                                                                                                                                  |

| J1                                   | GTXCLKd                                                      | SSTL_2 | input  | Channel d transmit clock. The rising edge of GTXCLKd clocks the input data into the Phase Align FIFO.                                                                                                                                                                                                                                                                                  |

| U9                                   | TXPd                                                         | CML    | output | Channel d differential serial data transmit. TXPd is the positive differential output pin of the channel d Line Driver. The TXPd and TXNd look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor.                                                                                                                      |

## **Pin Descriptions**

## CYP32G0401DX Transmitter Pins (53)<sup>[1]</sup> (continued)

| Pin | Name    | Level  | I/O    | Description                                                                                                                                                                                                                                                       |

|-----|---------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U8  | TXNd    | CML    | output | Channel d differential serial data transmit. TXNd is the negative differential output pin of the channel d Line Driver. The TXPd and TXNd look like a differential amplifier with each of the output drains connected to $V_{DD}$ through a 50 $\Omega$ resistor. |

| A11 | TCLKOUT | SSTL_2 | output | Reference transmit clock output. TCLKOUT is the word clock sig-<br>nal used to clock data out of the Transmit Phase Align FIFOs of<br>all four channels. TCLKOUT is derived directly from the Frequency<br>Synthesizer output.                                    |

## CYP32G0401DX Receiver Pins (76)<sup>[2]</sup>

| Pin                                          | Name                                                         | Level  | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|--------------------------------------------------------------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J18, J17<br>H18, G20<br>G19, H17<br>G18, F20 | RXD0a, RXD1a<br>RXD2a, RXD3a<br>RXD4a, RXD5a<br>RXD6a, RXD7a | SSTL_2 | outputs | Channel a receive data. The receive data RXDa[7:0] are clocked out of the Elasticity FIFO by RCLKINa.                                                                                                                                                                                                                                                                                                                           |

| F19                                          | RXERa                                                        | SSTL_2 | output  | Channel a receive error (RXERa) in <i>MODE 1</i> <sup>[2]</sup><br>Channel a receive data bit9 (RXD9a) in <i>MODE 2</i><br>Channel a receive invalid character flag (ERRa) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                        |

| F18                                          | RXDVa                                                        | SSTL_2 | output  | Channel a receive data valid (RXDVa) in <i>MODE 1</i><br>Channel a receive data bit8 (RXD8a) in <i>MODE 2</i><br>Channel a receive code-group select (RXKa) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                       |

| H19                                          | CRSa                                                         | SSTL_2 | output  | Channel a receive carrier sense indicate (CRSa) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel a receive idle code (IDLEa) in <i>MODE 3</i><br>Channel a receive frame pulse flag (FRPa) in <i>MODE 4</i>                                                                                                                                                                                                             |

| J19                                          | COLa                                                         | SSTL_2 | output  | Channel a receive collision indicate (COLa) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel a receive invalid character flag (ERRa) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                      |

| E20                                          | RXCLKa                                                       | SSTL_2 | output  | Channel a receive clock output reference. The RXCLKa pin out-<br>puts either a buffered RCLKINa, or the recovered clock. This is<br>determined by the status of LBEN on the rising edge of RESETN<br>as follows: LBEN = 0 selects the buffered RCLKINa; LBEN = 1<br>selects the recovered clock.                                                                                                                                |

| E19                                          | OOFa                                                         | SSTL_2 | input   | Not used in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Not used in <i>MODE 3</i><br>Channel a OOF indicate in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                  |

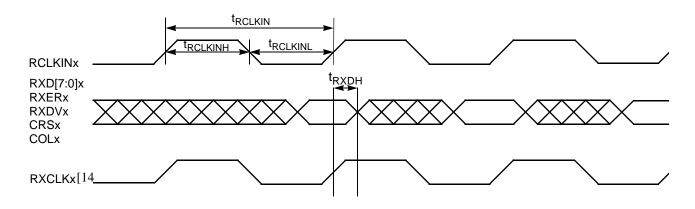

| H20                                          | RCLKINa                                                      | SSTL_2 | input   | Channel a receive Elasticity FIFO output clock. RCLKINa clocks the receive data RXDa[7:0], RXDVa, and RXERa out of the channel a Elasticity FIFO.                                                                                                                                                                                                                                                                               |

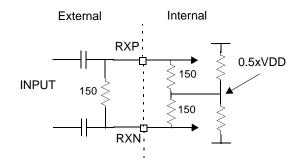

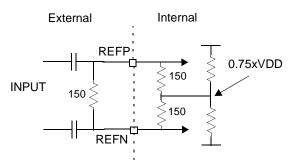

| W16                                          | RXPa                                                         | CML    | input   | Channel a serial receive data, ext. ac coupled, int. bias. RXPa is the positive differential input pin of the channel a Line Receiver. The RXPa and RXNa look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> . |

Note:

2. Receiver pins are **MODE**-dependent where indicated. See Table 1 for defined **MODES** of operation.

| Pin                                          | Name                                                         | Level  | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|--------------------------------------------------------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W15                                          | RXNa                                                         | CML    | input   | Channel a serial receive data, ext. ac coupled, int. bias. RXNa is the negative differential input pin of the channel a Line Receiver. The RXPa and RXNa look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| Y17                                          | LOSa                                                         | LVPECL | input   | Channel a receive loss of signal indicate. The signal input on the LOSa pin may come from a fiber module and indicates if there is a Loss of Signal (LOS) condition. If a LOS condition occurs, the data input is squelched and no data is sent to the data recovery block. When no data edges are present at the inputs to the clock recovery Digital Phase-Locked Loop (DPLL), its output frequency will be locked to the frequency of the transmit Frequency Synthesizer. The polarity of the LOSa signal is controlled by the POLa pin as shown in <i>Table 4</i> . |

| V17                                          | POLa                                                         | SSTL_2 | input   | Channel a receive loss of signal polarity. The POLa pin controls the polarity of the LOSa signal as shown in <i>Table 4</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D20, D19<br>D18, C17<br>B17, C16<br>B16, A16 | RXD0b, RXD1b<br>RXD2b, RXD3b<br>RXD4b, RXD5b<br>RXD6b, RXD7b | SSTL_2 | outputs | Channel b receive data. The receive data RXDb[7:0] are clocked out of the Elasticity FIFO by RCLKINb.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D16                                          | RXERb                                                        | SSTL_2 | output  | Channel b receive error (RXERb) in <i>MODE 1</i><br>Channel b receive data bit9 (RXD9b) in <i>MODE 2</i><br>Channel b receive invalid character flag (ERRb) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                               |

| B15                                          | RXDVb                                                        | SSTL_2 | output  | Channel b receive data valid (RXDVb) in <i>MODE 1</i><br>Channel b receive data bit8 (RXD8b) in <i>MODE 2</i><br>Channel B receive code-group select (RXKb) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                               |

| E18                                          | CRSb                                                         | SSTL_2 | output  | Channel b receive carrier sense indicate (CRSb) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel b receive idle code (IDLEb) in <i>MODE 3</i><br>Channel b receive frame pulse flag (FRPb) in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                     |

| E17                                          | COLb                                                         | SSTL_2 | output  | Channel b receive collision indicate (COLb) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel b receive invalid character flag (ERRb) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                                              |

| A17                                          | RXCLKb                                                       | SSTL_2 | output  | Channel b receive clock output reference. The RXCLKb pin out-<br>puts either a buffered RCLKINb, or the recovered clock. This is<br>determined by the status of LBEN on the rising edge of RESETN<br>as follows: LBEN = 0 selects the buffered RCLKINb; LBEN = 1<br>selects the recovered clock.                                                                                                                                                                                                                                                                        |

| F17                                          | OOFb                                                         | SSTL_2 | input   | Not used in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Not used in <i>MODE 3</i><br>Channel b OOF indicate in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A15                                          | RCLKINb                                                      | SSTL_2 | input   | Channel b receive Elasticity FIFO output clock. RCLKINb clocks the receive data RXDb[7:0], RXDVb, and RXERb out of the channel b Elasticity FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Y15                                          | RXPb                                                         | CML    | input   | Channel b serial receive data, ext. ac coupled, int. bias. RXPb is the positive differential input pin of the channel b Line Receiver. The RXPb and RXNb look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| Pin                                  | Name                                                         | Level  | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|--------------------------------------------------------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y14                                  | RXNb                                                         | CML    | input   | Channel b serial receive data, ext. ac coupled, int. bias. RXNb is the negative differential input pin of the channel b Line Receiver. The RXPb and RXNb look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| V16                                  | LOSb                                                         | LVPECL | input   | Channel b receive loss of signal indicate. The signal input on the LOSb pin may come from a fiber module and indicates if there is a Loss of Signal (LOS) condition. If a LOS condition occurs, the data input is squelched and no data is sent to the data recovery block. When no data edges are present at the inputs to the clock recovery Digital Phase-Locked Loop (DPLL), its output frequency will be locked to the frequency of the transmit Frequency Synthesizer. The polarity of the LOSb signal is controlled by the POLb pin as shown in <i>Table 4</i> . |

| Y16                                  | POLb                                                         | SSTL_2 | input   | Channel b receive loss of signal polarity. The POLb pin controls the polarity of the LOSb signal as shown in <i>Table 4</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B6, C6<br>A5, B5<br>C5, B4<br>D5, C4 | RXD0c, RXD1c<br>RXD2c, RXD3c<br>RXD4c, RXD5c<br>RXD6c, RXD7c | SSTL_2 | outputs | Channel c receive data. The receive data RXDc[7:0] are clocked out of the Elasticity FIFO by RCLKINc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D3                                   | RXERc                                                        | SSTL_2 | output  | Channel c receive error (RXERc) in <i>MODE 1</i><br>Channel c receive data bit9 (RXD9c) in <i>MODE 2</i><br>Channel c receive invalid character flag (ERRc) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                               |

| D2                                   | RXDVc                                                        | SSTL_2 | output  | Channel c receive data valid (RXDVc) in <i>MODE 1</i><br>Channel c receive data bit8 (RXD8c) in <i>MODE 2</i><br>Channel c receive code-group select (RXKc) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                               |

| D6                                   | CRSc                                                         | SSTL_2 | output  | Channel c receive carrier sense indicate (CRSc) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel c receive idle code (IDLEc) in <i>MODE 3</i><br>Channel c receive frame pulse flag (FRPc) in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                     |

| C7                                   | COLc                                                         | SSTL_2 | output  | Channel c receive collision indicate (COLc) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel c receive invalid character flag (ERRc) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                                              |

| A6                                   | RXCLKc                                                       | SSTL_2 | output  | Channel c receive clock output reference. The RXCLKc pin out-<br>puts either a buffered RCLKINc, or the recovered clock. This is<br>determined by the status of LBEN on the rising edge of RESETN<br>as follows: LBEN = 0 selects the buffered RCLKINc; LBEN = 1<br>selects the recovered clock.                                                                                                                                                                                                                                                                        |

| E4                                   | OOFc                                                         | SSTL_2 | input   | Not used in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Not used in <i>MODE 3</i><br>Channel c OOF indicate in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A4                                   | RCLKINc                                                      | SSTL_2 | input   | Channel c receive Elasticity FIFO output clock. RCLKINc clocks the receive data RXDc[7:0], RXDVc, and RXERc out of the channel c Elasticity FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Y7                                   | RXPc                                                         | CML    | input   | Channel c serial receive data, ext. ac coupled, int. bias. RXPc is the positive differential input pin of the channel c Line Receiver. The RXPc and RXNc look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| Pin                                  | Name                                                         | Level  | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|--------------------------------------------------------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y6                                   | RXNc                                                         | CML    | input   | Channel c serial receive data, ext. ac coupled, int. bias. RXNc is the negative differential input pin of the channel c Line Receiver. The RXPc and RXNc look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| V5                                   | LOSc                                                         | LVPECL | input   | Channel c receive loss of signal indicate. The signal input on the LOSc pin may come from a fiber module and indicates if there is a Loss of Signal (LOS) condition. If a LOS condition occurs, the data input is squelched and no data is sent to the data recovery block. When no data edges are present at the inputs to the clock recovery Digital Phase-Locked Loop (DPLL), its output frequency will be locked to the frequency of the transmit Frequency Synthesizer. The polarity of the LOSc signal is controlled by the POLc pin as shown in <i>Table 4</i> . |

| Y4                                   | POLc                                                         | SSTL_2 | input   | Channel c receive loss of signal polarity. The POLc pin controls the polarity of the LOSc signal as shown in <i>Table 4</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| H2, H3<br>G2, G3<br>F1, F2<br>F3, E2 | RXD0d, RXD1d<br>RXD2d, RXD3d<br>RXD4d, RXD5d<br>RXD6d, RXD7d | SSTL_2 | outputs | Channel d receive data. The receive data RXDd[7:0] are clocked out of the Elasticity FIFO by RCLKINd.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| F4                                   | RXERd                                                        | SSTL_2 | output  | Channel d receive error (RXERd) in <i>MODE 1</i><br>Channel d receive data bit9 (RXD9d) in <i>MODE 2</i><br>Channel d receive invalid character flag (ERRd) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                               |

| E3                                   | RXDVd                                                        | SSTL_2 | output  | Channel d receive data valid (RXDVd) in <i>MODE 1</i><br>Channel d receive data bit8 (RXD8d) in <i>MODE 2</i><br>Channel d receive code-group select (RXKd) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                               |

| J4                                   | CRSd                                                         | SSTL_2 | output  | Channel d receive carrier sense indicate (CRSd) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel d receive idle code (IDLEd) in <i>MODE 3</i><br>Channel d receive frame pulse flag (FRPd) in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                     |

| H4                                   | COLd                                                         | SSTL_2 | output  | Channel d receive collision indicate (COLd) in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Channel d receive invalid character flag (ERRd) in <i>MODE 3</i><br>Not used in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                                              |

| E1                                   | RXCLKd                                                       | SSTL_2 | output  | Channel d receive clock output reference. The RXCLKd pin out-<br>puts either a buffered RCLKINd, or the recovered clock. This is<br>determined by the status of LBEN on the rising edge of RESETN<br>as follows: LBEN = 0 selects the buffered RCLKINd; LBEN = 1<br>selects the recovered clock.                                                                                                                                                                                                                                                                        |

| D1                                   | OOFd                                                         | SSTL_2 | input   | Not used in <i>MODE 1</i><br>Not used in <i>MODE 2</i><br>Not used in <i>MODE 3</i><br>Channel d OOF indicate in <i>MODE 4</i>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| G1                                   | RCLKINd                                                      | SSTL_2 | input   | Channel d receive Elasticity FIFO output clock. RCLKINd clocks the receive data RXDd[7:0], RXDVd, and RXERd out of the channel d Elasticity FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| W6                                   | RXPd                                                         | CML    | input   | Channel d serial receive data, ext. ac coupled, int. bias. RXPd is the positive differential input pin of the channel d Line Receiver. The RXPd and RXNd look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| Pin | Name | Level  | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W5  | RXNd | CML    | input | Channel d serial receive data, ext. ac coupled, int. bias. RXNd is the negative differential input pin of the channel d Line Receiver. The RXPd and RXNd look like a differential amplifier with each of the input pins connected to $V_{DD}/2$ through a 150 $\Omega$ resistor. When inputs are differentially terminated with a 150 $\Omega$ resistor, the line termination is nominally 100 $\Omega$ . See <i>Figure 6</i> .                                                                                                                                         |

| U5  | LOSd | LVPECL | input | Channel d receive loss of signal indicate. The signal input on the LOSd pin may come from a fiber module and indicates if there is a Loss of Signal (LOS) condition. If a LOS condition occurs, the data input is squelched and no data is sent to the data recovery block. When no data edges are present at the inputs to the clock recovery Digital Phase-Locked Loop (DPLL), its output frequency will be locked to the frequency of the transmit Frequency Synthesizer. The polarity of the LOSd signal is controlled by the POLd pin as shown in <i>Table 4</i> . |

| V6  | POLd | SSTL_2 | input | Channel d receive loss of signal polarity. The POLd pin controls the polarity of the LOSd signal as shown in <i>Table 4</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# CYP32G0401DX Control pins (11)<sup>[3]</sup>

| Pin      | Name             | Level  | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N1       | RESETN           | SSTL_2 | Bidir | Chip global reset (active LOW bidirectional pull down). The RESETN pin reflects the operation of the Power On Reset (POR) circuit. When POR is active, RESETN is driven LOW. When POR is inactive, RESETN is three-stated and an internal pull-up resistor (approximately 50 k $\Omega$ ) establishes the inactive (HIGH) state. The RESETN pin may also be driven from an external device in order to re-initialize the chip regardless of the internal operating state and regardless of the state of POR. In this case RESETN must be driven LOW for a minimum of two cycles of the reference clock (REFP, REFN), though no other timing relationship between RESETN and the reference clock need exist. |

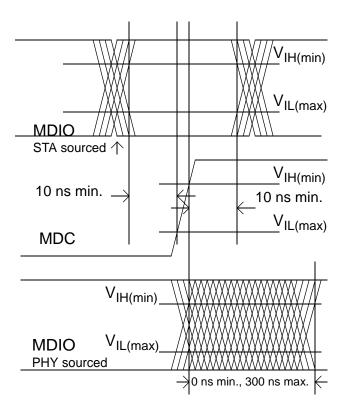

| P19      | MDC              | SSTL_2 | input | Management Interface Data Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| N17      | MDIO             | SSTL_2 | Bidir | Management Interface Data Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

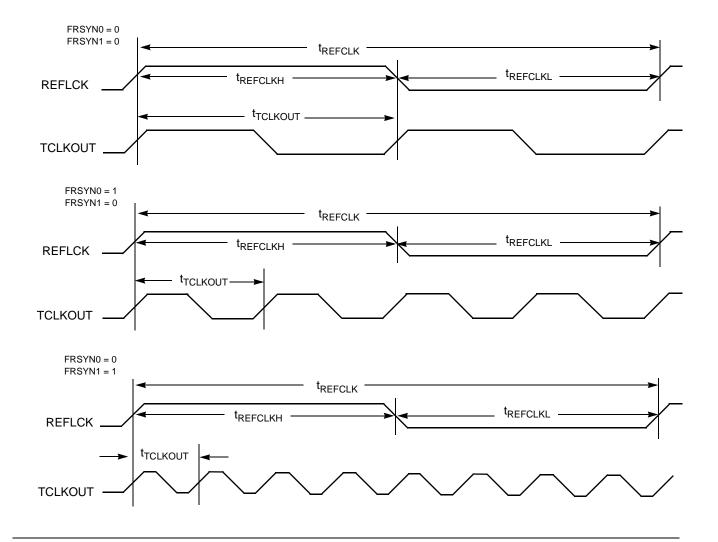

| N4<br>N3 | FRSYN0<br>FRSYN1 | SSTL_2 | input | Frequency Synthesizer PLL ratio select. The FRSYN0 and FRSYN1 pins, together with the SER8_10 pin, select from the allowable reference clock frequency ranges for input to the frequency synthesizer. See <i>Table 2</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V4       | SER8_10          | SSTL_2 | input | 8-bit (SER8_10 = 1), 10-bit (SER8_10 = 0) data select. <sup>[3]</sup> The parallel-to-serial and serial-to-parallel converters operate in two modes, eight-bit and ten-bit, under the control of the SER8_10 pin, as shown in <i>Table 3</i> . The 8-bit/10-bit selection made using the SER8_10 pin will also affect the choice of reference clock frequency range made using the FRSYN0 and FRSYN1 pins, as shown in <i>Table 2</i> .                                                                                                                                                                                                                                                                     |

| U2       | ENCODE           | SSTL_2 | input | Encode select. <sup>[3]</sup> The 8B/10B encode and decode functions are<br>enabled when ENCODE = 1. The encoder translates the 8-bit<br>input byte to a 10-bit symbol for transmit, and the decoder trans-<br>lates the received 10-bit symbol to the 8-bit byte originally en-<br>coded at the other end. Both encode and decode functions are<br>bypassed when ENCODE = 0.                                                                                                                                                                                                                                                                                                                               |

Note:

3. The control pins SER8\_10, ENCODE and FRAME together select the operating *MODE*. See *Table 1* for defined operating *MODES*.

# CYP32G0401DX Control pins (11)<sup>[3]</sup> (continued)

| Pin | Name  | Level  | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U3  | FRAME | SSTL_2 | input | Frame select. <sup>[3]</sup> The Ethernet PCS functions are enabled when<br>FRAME=1. This performs Ethernet PCS functions using the<br>IEEE802.3z ordered set state machine (Section 36.2.5.2.1 and<br>Figures 36-5 and 36-6) during transmit, and the receive and syn-<br>chronization state machines (Section 36.2.5.2.2 and Figures 36-<br>7a, 36-7b, 36-8, and 36-9) during receive.                                                                                                                                                                                     |

| U19 | LBEN  | SSTL_2 | input | Loop back enable. When loop back is enabled (LBEN = 1) both<br>the high-speed line side data and the byte input data are looped<br>back. The parallel input data (TXD[7:0], TXEN, TXER) are<br>looped back to the receive side parallel data (RXD[7:0], RXDV,<br>RXER), and the line-received data (RXP and RXN) are looped<br>back and sent to the line driver (TXP and TXN). In <i>MODE 1</i> the<br>transmit driver (TXP, TXN) is disabled, as required in IEEE802.3<br>Section 22.2.4.1.2. <b>Note:</b> LBEN is logically ORed with bit 0.14<br>of the control register. |

| R1  | REFP  | CML    | input | Differential Frequency Synthesizer clock input, externally ac coupled, internally biased. REFP is the positive differential input pin for the reference clock (REFCLK) used by the frequency synthesizer. The REFP and REFN look like a differential amplifier with each of the input pins connected to $0.75 \text{xV}_{\text{DD}}$ through a 150 $\Omega$ resistor. See <i>Table 7</i> .                                                                                                                                                                                   |

| Τ1  | REFN  | CML    | input | Differential Frequency Synthesizer clock input, externally ac coupled, internally biased. REFN is the negative differential input pin for the reference clock (REFCLK) used by the frequency synthesizer. The REFP and REFN look like a differential amplifier with each of the input pins connected to $0.75 \text{xV}_{\text{DD}}$ through a 150 $\Omega$ resistor. See <i>Table 7</i> .                                                                                                                                                                                   |

## CYP32G0401DX Analog Power Pins (65)

| Pin | Name  | Function     | Description                    |

|-----|-------|--------------|--------------------------------|

| Y10 | VFS1  | Analog Power | Frequency Synthesizer PLL VDD1 |

| W11 | VFS2  | Analog Power | Frequency Synthesizer PLL VDD2 |

| Y9  | VFS3  | Analog Power | Frequency Synthesizer PLL VDD3 |

| W10 | GFS1  | Analog Power | Frequency Synthesizer PLL GND1 |

| Y13 | GFS2  | Analog Power | Frequency Synthesizer PLL GND2 |

| W8  | GFS3  | Analog Power | Frequency Synthesizer PLL GND3 |

| W13 | VTXDa | Analog Power | Channel a transmit VDD1        |

| W17 | VTXMa | Analog Power | Channel a transmit VDD2        |

| V13 | GTXDa | Analog Power | Channel a transmit GND1        |

| U16 | GTXMa | Analog Power | Channel a transmit GND2        |

| U11 | VTXDb | Analog Power | Channel b transmit VDD1        |

| R17 | VTXMb | Analog Power | Channel b transmit VDD2        |

| W12 | GTXDb | Analog Power | Channel b transmit GND1        |

| T18 | GTXMb | Analog Power | Channel b transmit GND2        |

| W9  | VTXDc | Analog Power | Channel c transmit VDD1        |

| R2  | VTXMc | Analog Power | Channel c transmit VDD2        |

| U10 | GTXDc | Analog Power | Channel c transmit GND1        |

| P3  | GTXMc | Analog Power | Channel c transmit GND2        |

| W7  | VTXDd | Analog Power | Channel d transmit VDD1        |

| Т3  | VTXMd | Analog Power | Channel d transmit VDD2        |

| V8  | GTXDd | Analog Power | Channel d transmit GND1        |

## CYP32G0401DX Analog Power Pins (65) (continued)

| Pin | Name  | Function     | Description             |

|-----|-------|--------------|-------------------------|

| R4  | GTXMd | Analog Power | Channel d transmit GND2 |

| V15 | VRXDa | Analog Power | Channel a receive VDD1  |

| U18 | VRXMa | Analog Power | Channel a receive VDD2  |

| U15 | GRXDa | Analog Power | Channel a receive GND1  |

| T17 | GRXMa | Analog Power | Channel a receive GND2  |

| W14 | VRXDb | Analog Power | Channel b receive VDD1  |

| P18 | VRXMb | Analog Power | Channel b receive VDD2  |

| V14 | GRXDb | Analog Power | Channel b receive GND1  |

| U20 | GRXMb | Analog Power | Channel b receive GND2  |

| Y5  | VRXDc | Analog Power | Channel c receive VDD1  |

| R3  | VRXMc | Analog Power | Channel c receive VDD2  |

| V7  | GRXDc | Analog Power | Channel c receive GND1  |

| T2  | GRXMc | Analog Power | Channel c receive GND2  |

| W4  | VRXDd | Analog Power | Channel d receive VDD1  |

| T4  | VRXMd | Analog Power | Channel d receive VDD2  |

| U6  | GRXDd | Analog Power | Channel d receive GND1  |

| U1  | GRXMd | Analog Power | Channel d receive GND2  |

| P4  | AVDD  | Analog Power | General Analog VDD      |

| P17 | AVDD  | Analog Power | General Analog VDD      |